滤波,屏蔽,接地;众所周知是我们EMC设计的三大手法;其中接地设计是电子产品设计的一个重要问题!接地的目的如下:

A.接地可使我们的电路系统中的所有单元电路都有一个公共的参考0电位,也就是各个电路之间没有电位差,保证电路系统能稳定的工作;

B.防止外部的电磁干扰。比如机壳接地;为瞬态干扰(ESD)提供了泄放通道;也可使因静电感应而累积在机壳上的大量电荷通过大地泄放;如果电路有使用屏蔽罩或电路的屏蔽体,选择合适的接地,就能获得更好的屏蔽效果!

C.保证安全工作。当发生雷电(Surge)的电磁感应时,可避免电子设备损坏;

因此,接地对于EMS来说是抑制噪声,防止干扰的主要方法。接地可以理解为一个等电位点或者等电位面是电子线路系统的基准电位,但不一定为大地电位;为了防止雷击的损坏和保护产品&设备操作人员的安全,电子设备的机壳和供电系统的金属构件再必须与大地相连接!而且要求接地电阻很小,不能超过规定值。

大多数产品都有要求接地;虽然接地可以是真正的接地,隔离或者浮地但接地的结构必须存在。接地我们有时会与为信号提供电流的回路相混淆。实际中大部分的问题是与PCB设计有关的;对于复杂系统的问题有时可以归结为在模拟及数字电路之间提供参考连接及在PCB的地层和金属外壳之间提供高频连接的设计问题!

接地设计尽管是EMC设计中最重要的方面通常处理的问题并不容易直观理解;其实每一个电路最终都要有一个参考接地源,电路设计首先考虑到的是接地设计,接地是使不希望的噪声&干扰最小化 并对电路进行隔离划分的一个重要方法。PCB的接地及铺地铜设计降避免许多的噪声问题,设计良好的接地系统就是以低的成本来防止不希望有的干扰及发射。比如对于高速数字电路中的地平面不完整,连接电缆后由于被地平面上的噪声电压驱动,就会产生EMI的问题!

首先分享对接地电流的看法:

A.一旦有电流流过一定的阻抗,就会产生一定的电压降;利用欧姆定律在电子线路板上,就没有OV电位电压或电流的单位可能在微伏或微安级的范围内,存在一个较小的有限值。

B.电流总是要返回其源头来;回路可能有许多不同的路径,每条路径上的电流幅值不同,这会与该路径的阻抗有关。不希望某些电流在其中某条路径上流动,因此就需要在该路径上要采取抑制措施!

因此在进行产品设计时;首先考虑到接地是最经济的办法。在设计阶段若没有考虑,就意味着该系统在EMC方面有可能会失败。一个设计良好的接地系统;包含从电子线路的PCB设计,能从系统的角度防止EMI和EMS的问题才是关键的设计。

用下面的PCB铺地及时钟的接地设计案例进行分享关键设计:

电子产品中PCB布线铺地的设计,对于目前低成本的物联网及智能产品来说是众多的设计工程师采用的方法;由于产品系统中需要有晶振推动的MCU/CPU高频工作;PCB的铺地设计能给系统EMC设计带来优势!

双面板PCB系统铺地的理论和分析;铺铜地对EMI有什么影响?

铺地好的方面:

注意信号线的PCB板边缘的走线 如果铺地;这个信号线对外的信号耦合就减小了;PCB铺铜地在PCB板的边缘的地方就要有;铺铜铺在信号线之间,它就能降低信号间的串扰,串扰中的EMI辐射是跟它间接的关系的!如果两个都能达到或者做到了 EMI效果就会好!铺地不是每个地方按面积来数的,地要有目标的去铺设才会有好的作用的!

我的观点:PCB有铺铜的条件,且这个铺铜是有作用的,如果能提升EMI的性能;可建议采用PCB铺地铜的法则!

注意点:

在这个设计上要铺地就要保证信号的铺地平面与系统的参考地电位的阻抗要足够小;否则这个铺地就会对辐射干扰或抗辐射干扰都会有影响!

对于高频的应用电子产品线路;系统由于共模电流的干扰EMI的问题,我们在DC-DC直流电流输出端以及功能电路的接口连接器端需要增加共模电感及其组合的LCM*C的EMI滤波器的设计;此时的PCB铺地铜布局布线会对我们的高频EMI就会带来影响;分析参如下:

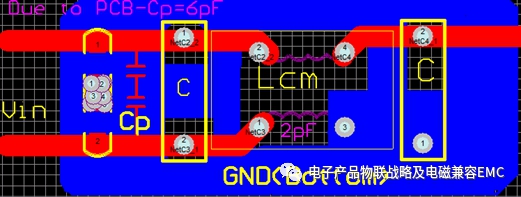

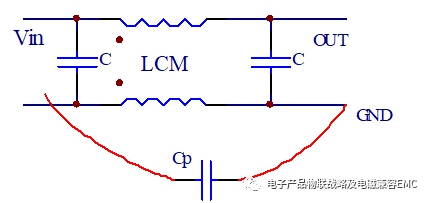

当电子线路中有共模电感的滤波设计时,前后级进行PCB铺地铜设计时TOP层的走线与BOTTOM底层的PCB铺地就会存在耦合电容Cp;高频的骚扰信号就会通过耦合电容影响共模电感的噪声阻抗性能;等效电路如下:

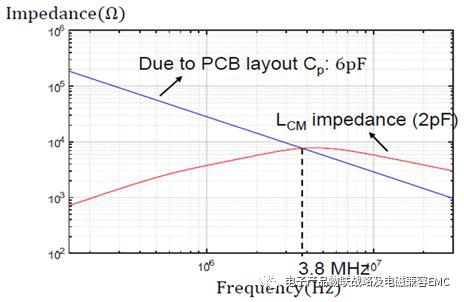

比如系统的设计LCM器件的杂散电容为2pF;其谐振频率点在4MHZ左右;进行PCB的铺地铜的设计由于PCB的布线,其输入的走线与PCB的铺地铜带来有6pF的耦合电容参数;分析如下:

在其LCM的谐振点后就会降低其阻抗值-如上图的频率&阻抗特性曲线参考数据;在进行EMI测试时就会带来高频>4MHZ的高频EMI的问题!

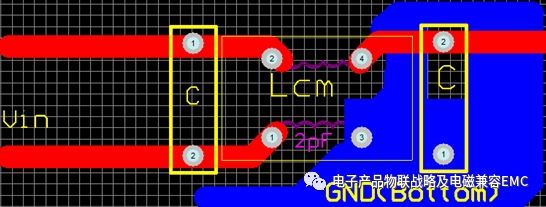

在进行PCB双面板布线铺铜地的设计时;在某些电路设计中改进PCB布局及走线就可以降低高频的EMI电磁干扰;简单优化的PCB设计参考如下:

注意:如果接地层存在噪声耦合源,则接地层不应靠近敏感输入电路。

对于双面板的系统有时钟信号是很普遍的;系统晶振时钟频率高,干扰谐波能量就强;干扰谐波除了从其输入与输出两条布局布线传导出来还会从空间辐射出来,若布局布线不合理,很容易产生很强的尖峰噪声辐射问题,因此在PCB 板布局布线时对晶振和CLK 信号线布局非常重要,高频时钟信号需要能镜像回流完整的铺地铜的设计是很关键的。

时钟源的布局布线简单说明如下:

A.对于有源晶振:耦合电容应尽量靠近晶振的电源引脚,位置摆放顺序:

按电源流入方向,依容值从大到小依次摆放,容值最小的电容最靠近引脚。

B.晶振的外壳必须接地,可将晶振信号源包地设计;防止向外辐射,也可以屏蔽外来信号对晶振的干扰。

C.晶振下面不要布其它走线,保证完全铺地,同时在晶振的300mil范围内不要布其它走线,防止晶振噪声源耦合到其它布线、器件等影响性能。

D.时钟信号的走线应尽量短,晶振不要放置在PCB板的边缘!

如果电路板边缘有复位及数据&地址信号线等等,PCB的板的边缘都需要进行铺地铜的设计;保证关键信号线的地回流路径的镜像对称性设计。

因此,对于PCB双面板的铺铜地不是每个地方按面积来铺设的,铺地要有目标的去铺设才能有好的作用,不正确的铺地设计反而会恶化系统的EMC性能。

|

||||||||||||||||||||||||

|

||||||||||||||||||||||||