当前位置:首 页 --> 方案设计

MCF51AG128三相BLDC马达控制设计方案

发布时间:2016/3/25 11:38:00 来源:

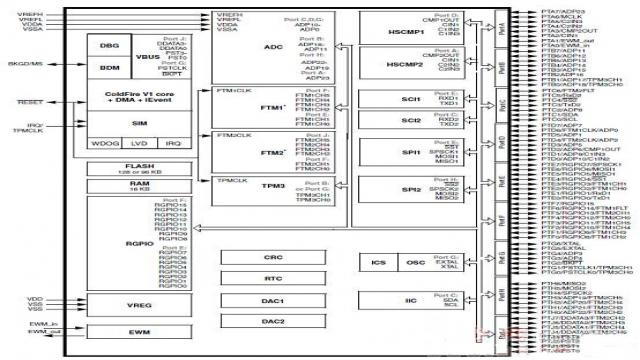

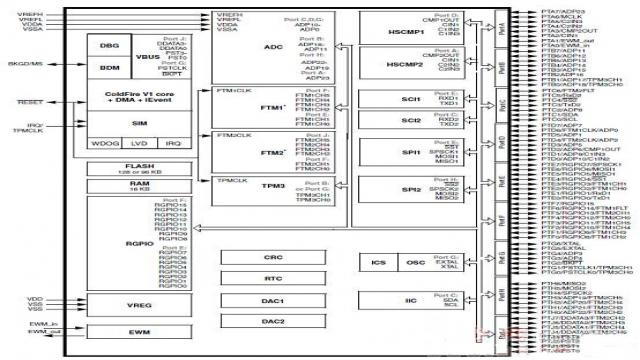

MCF51AG128是ColdFire系列32位可变长度精简指令集(RISC)微控制器。本文介绍了MCF51AG128系列MCU,重点介绍了高度集成且多样化的特性集。

MCF51AG128衍生品是低成本、低功耗、高性能32位ColdFire V1微控制器单元(MCU),专为工业和电器应用设计。它提升了基于MC9S08AC128系列8位微控制器的设计。

MCF51AG128主要特性

32位V1 ColdFire中央处理器单元(CPU)

工作电压为2.7V至5.5V、频率高达50.33MHz的ColdFire CPU

从内部RAM运行时,实现了0.94Dhrystone2.1 DMIPS/MHz的性能(从闪存运行时,实现了0.76DMIPS/MHz的性能)

实现了Coldfire指令集修订版C(ISA_C)

片上存储器

在整个工作电压和温度范围内实现了高达128KB的闪存读取/编程/擦除

16KB随机存取存储器(RAM)

安全电路,能够防止未授权访问RAM和闪存内容

节能模式

3种超低功耗停止模式和降低功率等待模式

外设时钟使能寄存器可将时钟禁用到未使用的模块上,从而降低了电流

系统保护

高级独立时钟看门狗(WDOG),具有多种特性,例如稳定的刷新机制、窗口模式、高粒化超时和快速超时测试,并且常常强制复位

其它外部看门狗监控器(EWM),有助于复位外部电路

低压检测,具有复位或中断功能

独立低压报警,具有可选跳变点

非法操作码和非法地址检测,具有复位功能

各个阵列的闪存模块保护,能够防止意外写入/擦除

硬件CRC模块,支持快速循环冗余校验

调试支持

单线式后台调试接口

实时调试支持,具有6个硬件断点(4个PC、1个地址对和1个数据),可以配置成1或2级触发器

片上跟踪缓冲器提供了可编程启动/停止记录条件

支持利用调试可视化总线进行实时程序(和可选部分数据)跟踪

DMA控制器

4个独立可编程DMA通道为直接在系统存储器和I/O外设之间传输数据提供了方法

DMA使能外设包括IIC、SCI、SPI、FTM、HSCMP、ADC、RTC和eGPIO,来自于这些外设的DMA请求可以配置成DMA源或iEvent输入

CF1_INTC

支持44个外设I/O中断请求和7个软件(1个/级)中断请求

中断请求源、等级和优先级之间的固定联系,最多2个请求可以重映射到最高的可屏蔽等级和优先级

各个中断源都有唯一的矢量编号

支持服务例程中断确认(软件IACK)读周期,提升了系统性能

能够屏蔽任何单个或所有中断源

系统时钟源

振荡器(XOSC)——环路控制皮尔斯振荡器;晶体或陶瓷谐振器的频率范围:31.25kHz~38.4kHz或1MHz~16MHz

内部时钟源(ICS)——锁频环(FLL)由内部或外部参考控制;可调内部参考实现了0.2%的分辨率和2%的偏差(1%@0~70℃)

外设

ADC 24个分辨率为12位的模拟输入;采用12、10或8位右对齐格式的输出;单次或连续转换(单次转换后,自动回到空闲状态);转换完成时的中断或DMA请求;在低功耗模式下运行,实现了噪声更低的操作;异步时钟源,实现了噪声更低的操作;可以从RTC、PDB或iEvent中选择异步硬件转换触发器;乒乓模式期间基于硬件触发器的双采样;片上温度传感器

PDB 16位分辨率,带有预定标器;7个触发事件输入;触发事件信号的正跳变启动计数器;支持连续触发或单次、旁路模式;同时支持2个触发延迟输出或Ored;脉冲输出可用于HSCMP加窗信号

iEvent用户可编程组合布尔输出,将4条所选iEvent输入通道用作中断请求、DMA传输请求或硬件触发器

FTM 2个6通道灵活定时器/PWM模块,具有DMA请求选项;各个互补通道对都具有死区时间插入功能;通道与对等的输出一起成对运行,具有互补输出或独立通道(具有独立输出);16位自由运行计数器;可以同步加载具有写缓冲器的FTM寄存器;关键寄存器的写保护;与TPM后向兼容

TPM 16位自由运行或模数增/减计数操作;2条通道,每条通道都可以是输入采集、输出比较或边沿对齐PWM;每条通道1个中断 + 终端计数中断

CRC 高速硬件CRC发生器电路,采用16位移位寄存器;CRC16-CCITT符合x16+x12+x5+1多项式;所有单、双、奇数和大多数多位误差的误差检测;可编程初始晶粒值

HSCMP 2个模拟比较器,比较器输出的上升沿、下降沿或任意一个边沿上具有可选中断;比较器的正和负输入均来自于4:1多路复用器;可编程电压参考来自于2个内部DAC;支持DMA传输

I2C与I2C总线标准和SMBus V2特性兼容;100kbps@最高总线负载;多主操作;可以针对64个差分串行时钟频率之一对软件进行编程;可编程从地址和消抖输入滤波器;中断驱动逐字节数据传输;仲裁丢失中断和自动模式切换;调用地址识别中断;总线繁忙检测;广播和10位地址扩展;MCU处于Stop3模式时,地址匹配会导致唤醒;DMA支持

SCI 2个串行通信接口模块,具有可选13位中断;全双工、标准不归零(NRZ)格式;双缓冲发射器和接收器,具有独立使能;13位波特率选择,具有/32分数除法;中断驱动或轮询操作;硬件奇偶发生与校验;可编程8位或9位字长;接收器被空闲线路或地址符号唤醒;接收器的地址匹配特性降低了地址符号唤醒ISR开销;1/16位时间噪声检测;用于发射与接收的DMA传输

SPI 2个串行外设接口,具有全双工或单线式双向选项;双缓冲发射器与接收器;主或从模式操作;可选MSB优先或LSB优先移位;8位或16位数据模式;可编程发射比特率;接收数据缓冲器硬件匹配特性;用于发射与接收的DMA传输

输入/输出

69个GPIO和1个仅输入引脚

中断或DMA请求,所有输入引脚上的极性均可选

所有输入引脚上均具有可编程消抖滤波器、迟滞和可配置上拉/下拉器件

所有输出引脚上的转换速率和驱动力均可配置

独立引脚数值寄存器,能够读取数字引脚上的逻辑电平

16个快速通用I/O(RGPIO)引脚,连至处理器的本地32位平台总线,具有设置、清空和高速切换功能

图1 MCF51AG128系列MCU框图

BLDC马达没有换向器,因此比DC马达更可靠。BLDC马达还优于AC感应马达。因为它利用转子磁铁产生转子磁通量而实现了更高的效率,所以BLDC马达被应用到了高端白家电(例如冰箱、洗衣机、洗碗机)、高端泵、风扇和其它需要高可靠性与效率的应用之中。

图2 采用MCF51AG128无传感器三相BLDC马达演示板外形图

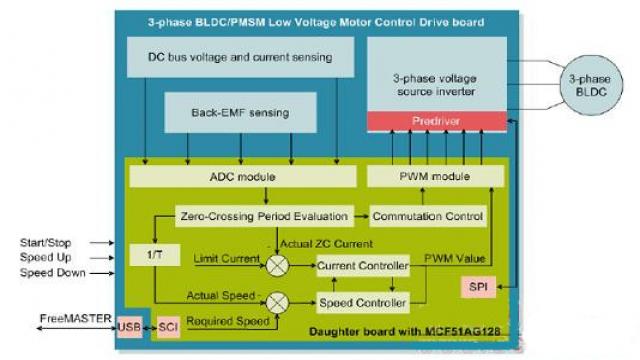

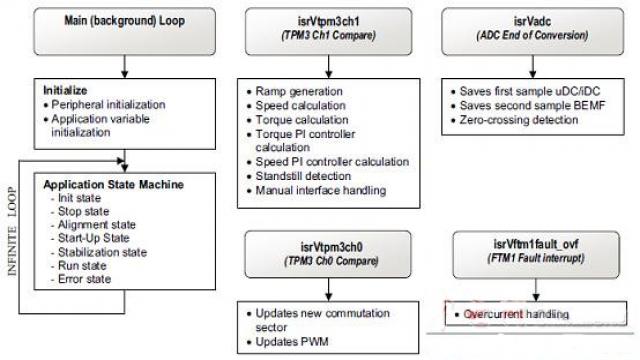

马达控制系统设计用于驱动组合速度/转矩闭环内的三相无刷DC马达(BLDC马达)。应用满足下列性能规范:

通过反EMF过零感应实现无传感器无刷DC马达控制

面向MCF51AGx平台

在低压(24V)三相马达控制驱动板上运行

控制技术:

利用组合速度/转矩闭环实现无传感器控制

利用ADC实现过零感应

沿2个方向旋转

全四象限操作

通过马达对齐从任何马达位置启动

手动接口(方向切换、上/下按钮控制)

免费MASTER软件控制接口(马达运行/停止、速度/转矩设置)

免费MASTER软件远程监控器

MCU初始化由器件初始化工具完成(Processor Expert的一部分)

MCF51AG128衍生品是低成本、低功耗、高性能32位ColdFire V1微控制器单元(MCU),专为工业和电器应用设计。它提升了基于MC9S08AC128系列8位微控制器的设计。

MCF51AG128主要特性

32位V1 ColdFire中央处理器单元(CPU)

工作电压为2.7V至5.5V、频率高达50.33MHz的ColdFire CPU

从内部RAM运行时,实现了0.94Dhrystone2.1 DMIPS/MHz的性能(从闪存运行时,实现了0.76DMIPS/MHz的性能)

实现了Coldfire指令集修订版C(ISA_C)

片上存储器

在整个工作电压和温度范围内实现了高达128KB的闪存读取/编程/擦除

16KB随机存取存储器(RAM)

安全电路,能够防止未授权访问RAM和闪存内容

节能模式

3种超低功耗停止模式和降低功率等待模式

外设时钟使能寄存器可将时钟禁用到未使用的模块上,从而降低了电流

系统保护

高级独立时钟看门狗(WDOG),具有多种特性,例如稳定的刷新机制、窗口模式、高粒化超时和快速超时测试,并且常常强制复位

其它外部看门狗监控器(EWM),有助于复位外部电路

低压检测,具有复位或中断功能

独立低压报警,具有可选跳变点

非法操作码和非法地址检测,具有复位功能

各个阵列的闪存模块保护,能够防止意外写入/擦除

硬件CRC模块,支持快速循环冗余校验

调试支持

单线式后台调试接口

实时调试支持,具有6个硬件断点(4个PC、1个地址对和1个数据),可以配置成1或2级触发器

片上跟踪缓冲器提供了可编程启动/停止记录条件

支持利用调试可视化总线进行实时程序(和可选部分数据)跟踪

DMA控制器

4个独立可编程DMA通道为直接在系统存储器和I/O外设之间传输数据提供了方法

DMA使能外设包括IIC、SCI、SPI、FTM、HSCMP、ADC、RTC和eGPIO,来自于这些外设的DMA请求可以配置成DMA源或iEvent输入

CF1_INTC

支持44个外设I/O中断请求和7个软件(1个/级)中断请求

中断请求源、等级和优先级之间的固定联系,最多2个请求可以重映射到最高的可屏蔽等级和优先级

各个中断源都有唯一的矢量编号

支持服务例程中断确认(软件IACK)读周期,提升了系统性能

能够屏蔽任何单个或所有中断源

系统时钟源

振荡器(XOSC)——环路控制皮尔斯振荡器;晶体或陶瓷谐振器的频率范围:31.25kHz~38.4kHz或1MHz~16MHz

内部时钟源(ICS)——锁频环(FLL)由内部或外部参考控制;可调内部参考实现了0.2%的分辨率和2%的偏差(1%@0~70℃)

外设

ADC 24个分辨率为12位的模拟输入;采用12、10或8位右对齐格式的输出;单次或连续转换(单次转换后,自动回到空闲状态);转换完成时的中断或DMA请求;在低功耗模式下运行,实现了噪声更低的操作;异步时钟源,实现了噪声更低的操作;可以从RTC、PDB或iEvent中选择异步硬件转换触发器;乒乓模式期间基于硬件触发器的双采样;片上温度传感器

PDB 16位分辨率,带有预定标器;7个触发事件输入;触发事件信号的正跳变启动计数器;支持连续触发或单次、旁路模式;同时支持2个触发延迟输出或Ored;脉冲输出可用于HSCMP加窗信号

iEvent用户可编程组合布尔输出,将4条所选iEvent输入通道用作中断请求、DMA传输请求或硬件触发器

FTM 2个6通道灵活定时器/PWM模块,具有DMA请求选项;各个互补通道对都具有死区时间插入功能;通道与对等的输出一起成对运行,具有互补输出或独立通道(具有独立输出);16位自由运行计数器;可以同步加载具有写缓冲器的FTM寄存器;关键寄存器的写保护;与TPM后向兼容

TPM 16位自由运行或模数增/减计数操作;2条通道,每条通道都可以是输入采集、输出比较或边沿对齐PWM;每条通道1个中断 + 终端计数中断

CRC 高速硬件CRC发生器电路,采用16位移位寄存器;CRC16-CCITT符合x16+x12+x5+1多项式;所有单、双、奇数和大多数多位误差的误差检测;可编程初始晶粒值

HSCMP 2个模拟比较器,比较器输出的上升沿、下降沿或任意一个边沿上具有可选中断;比较器的正和负输入均来自于4:1多路复用器;可编程电压参考来自于2个内部DAC;支持DMA传输

I2C与I2C总线标准和SMBus V2特性兼容;100kbps@最高总线负载;多主操作;可以针对64个差分串行时钟频率之一对软件进行编程;可编程从地址和消抖输入滤波器;中断驱动逐字节数据传输;仲裁丢失中断和自动模式切换;调用地址识别中断;总线繁忙检测;广播和10位地址扩展;MCU处于Stop3模式时,地址匹配会导致唤醒;DMA支持

SCI 2个串行通信接口模块,具有可选13位中断;全双工、标准不归零(NRZ)格式;双缓冲发射器和接收器,具有独立使能;13位波特率选择,具有/32分数除法;中断驱动或轮询操作;硬件奇偶发生与校验;可编程8位或9位字长;接收器被空闲线路或地址符号唤醒;接收器的地址匹配特性降低了地址符号唤醒ISR开销;1/16位时间噪声检测;用于发射与接收的DMA传输

SPI 2个串行外设接口,具有全双工或单线式双向选项;双缓冲发射器与接收器;主或从模式操作;可选MSB优先或LSB优先移位;8位或16位数据模式;可编程发射比特率;接收数据缓冲器硬件匹配特性;用于发射与接收的DMA传输

输入/输出

69个GPIO和1个仅输入引脚

中断或DMA请求,所有输入引脚上的极性均可选

所有输入引脚上均具有可编程消抖滤波器、迟滞和可配置上拉/下拉器件

所有输出引脚上的转换速率和驱动力均可配置

独立引脚数值寄存器,能够读取数字引脚上的逻辑电平

16个快速通用I/O(RGPIO)引脚,连至处理器的本地32位平台总线,具有设置、清空和高速切换功能

图1 MCF51AG128系列MCU框图

BLDC马达没有换向器,因此比DC马达更可靠。BLDC马达还优于AC感应马达。因为它利用转子磁铁产生转子磁通量而实现了更高的效率,所以BLDC马达被应用到了高端白家电(例如冰箱、洗衣机、洗碗机)、高端泵、风扇和其它需要高可靠性与效率的应用之中。

图2 采用MCF51AG128无传感器三相BLDC马达演示板外形图

马达控制系统设计用于驱动组合速度/转矩闭环内的三相无刷DC马达(BLDC马达)。应用满足下列性能规范:

通过反EMF过零感应实现无传感器无刷DC马达控制

面向MCF51AGx平台

在低压(24V)三相马达控制驱动板上运行

控制技术:

利用组合速度/转矩闭环实现无传感器控制

利用ADC实现过零感应

沿2个方向旋转

全四象限操作

通过马达对齐从任何马达位置启动

手动接口(方向切换、上/下按钮控制)

免费MASTER软件控制接口(马达运行/停止、速度/转矩设置)

免费MASTER软件远程监控器

MCU初始化由器件初始化工具完成(Processor Expert的一部分)

|

||||||

|

||||||