当前位置:首 页 --> 方案设计

如何降低便携式设备的待机功耗

发布时间:2015/11/18 14:15:00 来源:

随着蜂窝电话、PDA等便携式电子设备的功能不断增多,其设计复杂性也日益增加,这些设备在工作或待机时的系统功耗都不断上升。便携式设备的电源管理设计面临新的挑战,尤其是在内核电压、能耗管理和电池寿命等方面。

处理器内核在全功率模式下的功耗与工作频率和Vcore2成比例。根据处理器的工作频率,内核电压可被动态和精确地调节到较低限值,从而达到降低功耗的目的。

在待机模式下,由于微处理器或DSP的内核通常呈阻抗特性,因此电源管理没有在全功率模式下那么复杂。电压主要用于维持存储器和寄存器的状态。由于较新的内核设计都采用较低的电压,因此消耗的电流也较少,可以显著改善待机时的功耗。

本文将介绍如何利用非常简单的电压调节技术以及Micrel公司MIC2214芯片上的TTL兼容逻辑输入来有效地降低待机时的功耗。

用于蜂窝电话和PDA基带及DSP的双LDO

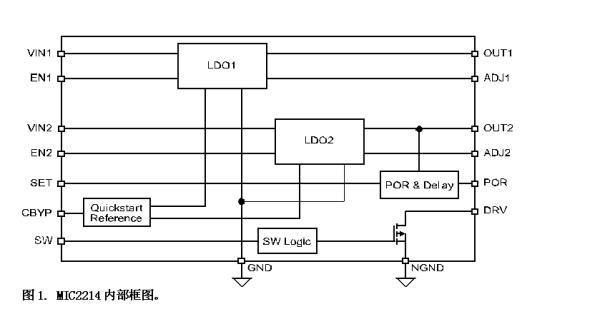

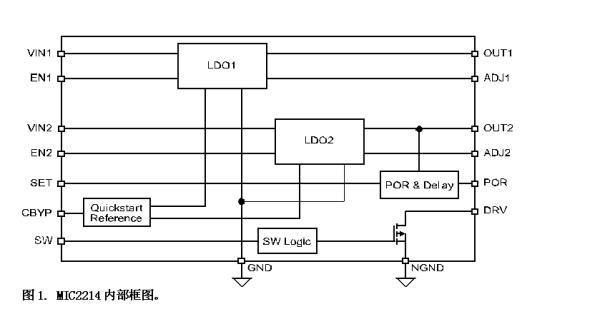

MIC2214是一个带有开漏驱动器和上电复位电路的双 μCap低压降线性调节器。第一个稳压器可以提供150mA的电流,第二个稳压器最多可以提供300mA电流,并包含上电复位功能。MIC2214的地电流非常低,每个LDO只有24μA。MIC2214有一个兼容TTL逻辑的使能引脚,可使芯片进入零关断模式电流状态,因此在不工作时几乎不消耗电流。固定电压输出的MIC2214采用3 x 3 MLF 封装,而可调电压输出的MIC2214则采用4 x 4 MLF 封装形式。

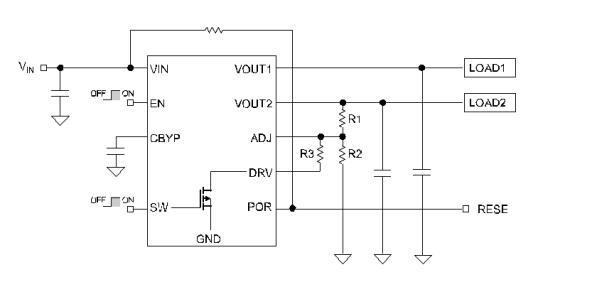

图1是带可调输出电压的MIC2214内部方框图。SW引脚在内部驱动一个NMOS门。当SW低时,DRV开路;当SW高时,DRV短接到地。

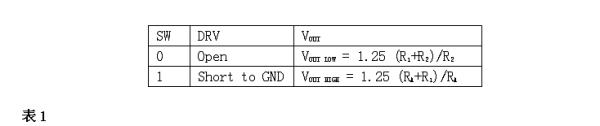

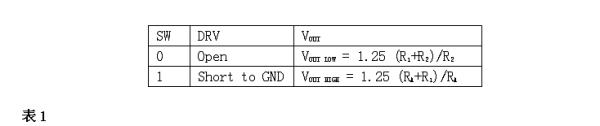

利用MIC2214可实现输出电压调节,电路如图2所示。通过将TTL兼容的SW引脚置高或置低,输出电压可以在两个输出电压值之间变化(见表1)。

SW

DRV

VOUT

0

Open

VOUT LOW = 1.25 (R1+R2)/R2

1

Short to GND

VOUT HIGH = 1.25 (RA+R1)/RA

其中Eq1:RA = R2*R3/(R2+R3)

采用以下电阻值时对上述电路进行测试。

R1= 50kΩ

R2= 255kΩ

R3= 210kΩ

集成在MIC2214内的开关(参考图2)具有几百毫欧级的RDS(开),因此在计算输出电压时可以忽略不计。不过在选择电阻时,应仔细选用阻值在100kΩ范围内的的电阻。如采用上述R1、R2和R3的阻值,将得到:

Vout low = 1.5V

以及 Vout high= 1.8V

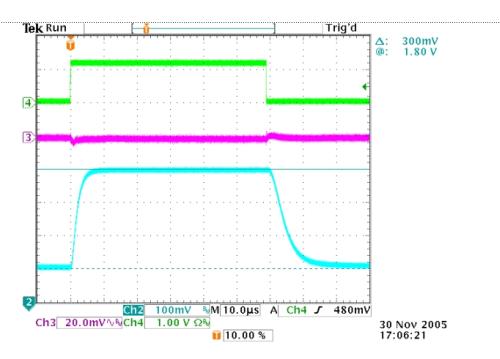

图3所示当SW引脚置高时,输出电压从1.5V到1.8V的变化。

如前所述,数字处理器的内核在待机状态时呈阻性。如果内核上加1.8V电压,并且只需1mA的载流,那么阻抗就是1800Ω。当内核加1.5V电压,需要电流则更小。功耗也因此从1.8mW下降到1.25mW,下降幅度达30%,从而可以延长30%的待机时间。

总之,随着便携式设备中新功能的不断增加,节省功率的创新设计解决方案将变得越来越重要。此外,对更长通话和运行时间的需求将驱动消费者的购买选择和一些关键任务的设计选择。本文讨论的技术可以成功运用于待机时间超过80%的基带处理器。该技术同样可以满足那些必须工作,但又有很多时间处于待机状态的应用处理器的内核电压要求,例如照相机加速器DSP。

处理器内核在全功率模式下的功耗与工作频率和Vcore2成比例。根据处理器的工作频率,内核电压可被动态和精确地调节到较低限值,从而达到降低功耗的目的。

在待机模式下,由于微处理器或DSP的内核通常呈阻抗特性,因此电源管理没有在全功率模式下那么复杂。电压主要用于维持存储器和寄存器的状态。由于较新的内核设计都采用较低的电压,因此消耗的电流也较少,可以显著改善待机时的功耗。

本文将介绍如何利用非常简单的电压调节技术以及Micrel公司MIC2214芯片上的TTL兼容逻辑输入来有效地降低待机时的功耗。

用于蜂窝电话和PDA基带及DSP的双LDO

MIC2214是一个带有开漏驱动器和上电复位电路的双 μCap低压降线性调节器。第一个稳压器可以提供150mA的电流,第二个稳压器最多可以提供300mA电流,并包含上电复位功能。MIC2214的地电流非常低,每个LDO只有24μA。MIC2214有一个兼容TTL逻辑的使能引脚,可使芯片进入零关断模式电流状态,因此在不工作时几乎不消耗电流。固定电压输出的MIC2214采用3 x 3 MLF 封装,而可调电压输出的MIC2214则采用4 x 4 MLF 封装形式。

图1是带可调输出电压的MIC2214内部方框图。SW引脚在内部驱动一个NMOS门。当SW低时,DRV开路;当SW高时,DRV短接到地。

利用MIC2214可实现输出电压调节,电路如图2所示。通过将TTL兼容的SW引脚置高或置低,输出电压可以在两个输出电压值之间变化(见表1)。

SW

DRV

VOUT

0

Open

VOUT LOW = 1.25 (R1+R2)/R2

1

Short to GND

VOUT HIGH = 1.25 (RA+R1)/RA

其中Eq1:RA = R2*R3/(R2+R3)

采用以下电阻值时对上述电路进行测试。

R1= 50kΩ

R2= 255kΩ

R3= 210kΩ

|

|

图2:利用MIC2214调节输出电压。 |

集成在MIC2214内的开关(参考图2)具有几百毫欧级的RDS(开),因此在计算输出电压时可以忽略不计。不过在选择电阻时,应仔细选用阻值在100kΩ范围内的的电阻。如采用上述R1、R2和R3的阻值,将得到:

Vout low = 1.5V

以及 Vout high= 1.8V

图3所示当SW引脚置高时,输出电压从1.5V到1.8V的变化。

|

| 图3:SW引脚置高时(CH4),输出电压从1.5V到1.8V的变化。 |

如前所述,数字处理器的内核在待机状态时呈阻性。如果内核上加1.8V电压,并且只需1mA的载流,那么阻抗就是1800Ω。当内核加1.5V电压,需要电流则更小。功耗也因此从1.8mW下降到1.25mW,下降幅度达30%,从而可以延长30%的待机时间。

总之,随着便携式设备中新功能的不断增加,节省功率的创新设计解决方案将变得越来越重要。此外,对更长通话和运行时间的需求将驱动消费者的购买选择和一些关键任务的设计选择。本文讨论的技术可以成功运用于待机时间超过80%的基带处理器。该技术同样可以满足那些必须工作,但又有很多时间处于待机状态的应用处理器的内核电压要求,例如照相机加速器DSP。

|

||||||

|

||||||