数模混合信号电路的低功耗设计

1、集成电路的低功耗设计动因

在集成电路发展的早期到上世纪八十年代,功耗问题并不是很突出。在这段时间内,由于电路系统规模普遍较小和CMOS工艺的兴起,低功耗尚未被作为IC设计的重要因素。

在1968年,Intel公司的创始人之一G. Moore就预测,每18到24个月,IC的集成度将提高一倍,这就是著名的Moore定律。而事实上,这四十多年来,IC技术就是基本上遵循着Moore定律取得了巨大的发展。集成电路经历了从小规模集成(SSI)发展到超大规模(VLSI)到现在的甚大规模集成(ULSI),即一个芯片上可以包含一亿以上的元件的水平。虽然量子效应和经济的限制将使IC集成度增长的速度趋缓,但是可以预见的是,随着新技术的采用IC的集成度持续发展的势头将不会改变。同时,系统的复杂度也在不断地提高,即将不同功能的器件和电路都集成到一个芯片上,构成一个系统集成芯片(SOC)。显然,集成电路复杂度和集成度的提高使得低功耗正成为一个不可或缺的电路设计指标。

首先,过高的功耗将使芯片容易过热,电路可靠性下降,最终导致失效。有研究表明,温度每升高10 C,器件的故障率将提高两倍;另外,不断增高的功耗将给芯片的封装和散热提出了更高的要求,这不仅会增加成本,而且在小型化应用场合中,这种方案往往不被采纳。

更重要的是,消费类电子产品的发展和大量应用推动了对功耗问题的研究。

低功耗的概念是由电子手表等工业首次提出的,而在小型化、高集成度的消费类电子产品中,为了降低电路成本、提高电路稳定性、可靠性,更需要设计低功耗电路,以保证在集成度提高时,单位面积维持同样甚至更低的功耗。同时,因为在过去的三十年中电池的容量仅仅增加了2~4倍,远没有VLSI技术的发展迅速,所以在电池供电系统中,集成电路的低功耗设计是延长电池使用寿命的最有效手段。此外,便携式设备趋于使用更少的电池,以减小尺寸和重量,也必然要求电路实现低功耗。和十年前相比,消费类电子产品在电子产业中的比例已从40%快速增长到55%,因此可以说消费类电子产品是低功耗设计的主要推动力。

2、数模混合信号电路的低功耗研究

在这种技术需求和便携式电子产品的应用需求的强烈推动下,CMOS集成电路低压低功耗设计受到了人们的极大重视。目前,人们对集成电路的功耗研究,主要集中在以下两个方面:

一是低功耗工艺的研究。这主要集中在减小特征尺寸、降低电源电压和降低阈值电压方面。减小特征尺寸,有助于将复杂系统集成在同一芯片上,进行有效地功耗管理。但是当特征尺寸缩小到一定程度,热载流子效应、动态节点的软失效将极大地影响着器件的性能,降低电源电压成为解决上述问题的较好方案。为了保证低压逻辑电路的驱动电流不减少和工作频率不降低,在降低电源电压的同时也要求降低阈值电压,但是同比例降低阈值电压会使漏泄电流指数级增加。采用多阈值电压器件或是采用可变阈值电压技术有望减小漏泄电流引起的功耗,而这些技术都比较依赖制造工艺。

二是低功耗设计方法的研究。这是目前低功耗研究中最为活跃的领域。在工艺确定的情况下,它包括低功耗的设计方法及评估方法,但主要是针对数字电路。

在保证系统同样性能的前提下,在芯片设计的初期,就从各个层次对功耗进行分析优化,不仅能够缩短设计周期,还能够实现整体功耗最小化目标。从设计的角度,低功耗设计方法可以分成系统级(System Level)、算法/结构(Architecture/Algorithm Level)、寄存器传输级(Register Transfer Level,RTL)、逻辑/门级(Logic/Gate Level)、版图级(Layout Level)这几个层次。其中,系统及算法作为低功耗技术中的高层次,对系统功耗的影响很大。在这种层次上的功耗分析将能对系统功耗进行预测及优化,并能实现几个数量级的功耗降低,因此必须加以重视。

有效的功耗评估工具和方法是低功耗研究的另一个重要内容。如何在设计的不同层次对电路功耗进行快速准确地估计,也是集成电路设计中的一个热点和难点问题。通常,把功耗评估分为基于随机统计和模拟的方法这两类。

基于随机统计的功耗估算方法,其基本思想为:先根据模块的版图或逻辑描述,抽取电路或逻辑模型,然后用随机产生的输入流模拟,计算平均功耗。

它的优点是速度较快,而且不需要电路内部信息,但功耗估算准确程度不及基于模拟的方法,因此适用于通常设计的早期阶段。

基于模拟的功耗估算方法是用一组典型的输入矢量进行功耗模拟,以获得平均功耗、最大功耗及最小功耗值。基于模拟的方法精度高,但所占存储空间和模拟时间较大,因此可以用一些启发信息来加速收敛,如蒙特卡罗(Monte Carlo)

模拟方法和遗传算法。其中,蒙特卡罗方法是在电路输入端随机产生输入信号,再用模拟方法计算在某一时间间隔内的功耗。如果将现有的电路级、门级等模拟方法用于蒙特卡罗程序的内环,将能够实现速度和计算精度的折衷。典型的基于模拟方法的功耗分析软件有POWERMILL、Entice-Aspen等。

需要指出的是,目前的低功耗研究大多是对模拟和数字电路进行分开讨论。这和模拟电路自身的特点密切相关。模拟集成电路和处理0或1信号的数字电路不同,它主要处理幅度、时间、频率连续变化的信号,并且具有以下特点:

①电路形式的多样性。包括数据转换器(如A/D转换器、D/A转换器等)、运算放大器、线性放大器(低噪声放大器、宽带放大器等)、非线性放大器(模拟乘法器、对数/反对数放大器等)、多路模拟开关、电源电压调节器(线性调压器、开关电源控制器等)、智能功率IC以及各类专用IC.

②性能指标的多样性。包括精度、输入范围、失真、噪声、电源电压抑制比(PSRR)、增益、频率带宽、输入/出阻抗等。

③电路结构的多样性。仅以一个运放为例,就有两级、Cascode、折叠式(Folded)Cascode、A/AB类放大器、单端/差分放大器等众多结构。

④器件的多样性。常见的器件就有晶体管、二极管、电阻、电容、甚至电感等。

模拟电路处理信号的连续性、电路结构形式的多样性、性能指标的精确性,都使得电路及版图的设计必须围绕具体电路展开,设计的自动化程度远远低于数字电路,而难度又远高于后者。

虽然在数字时代,数字电路的设计方法、工艺条件都领先于模拟电路,数字IC的市场占有率也要高于模拟IC,但模拟电路毕竟是数字电路和现实世界的桥梁,所以它仍然有足够的发展空间。另外,在实际的较高复杂度的系统中,总是把存储电路、逻辑控制电路和模拟电路一起集成在同一芯片中,即所谓的数模混合电路。CMOS工艺的成熟和在数字电路中的普遍应用,也要求系统中模拟电路工艺要和标准CMOS工艺相容,因此,模拟电路中包括功耗在内的性能将直接决定着系统的性能。

在混合信号电路中,许多成功应用在数字电路中的低功耗技术,并不适合应用在模拟电路中。例如,降低电源电压是减小功耗的有效方法,但对于模拟电路,给定的动态范围、增益和增益带宽乘积,降低电源电压将反而使功耗升高,这同时也说明,在低电压下实现低功耗,是以牺牲电路的一部分性能为代价的。因为模拟电路的性能不能脱离具体的电路来讨论,所以有较多的文献报道了低压低功耗电路设计。

随着越来越多的电池供电数模混合电路的出现,上述传统的设计方法受到了强烈的挑战。低功耗必然要求对整个混合信号电路进行统一的功耗管理,而不是将模拟、数字电路孤立开来。从设计的角度,如何协同考虑数字、模拟电路的功耗,会遇到比纯数字电路或纯模拟电路更多的困难。

锂离子电池管理芯片的应用及发展

1、锂离子电池的特点及应用

早在1912年,以金属锂作为电极的锂电池(Li Battery)的研究就开始了,到上世纪七十年代,不可充电的锂电池才首次应用在商业领域。上世纪八十年代,研究的重点集中在可充电的锂离子电池(Li-ion Battery)上,但并没有成功解决电池的安全性问题。一直到1991年,Sony公司首次实现了锂离子电池商业化,被认为是能源技术领域的一个重要的里程牌。

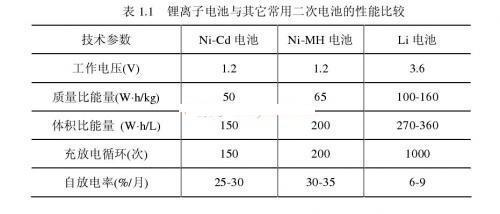

如表1.1所示,和Ni-Cd等其它二次电池相比,锂离子电池具有更高的能量密度(包括质量比能量和体积比能量)、更高的充放电循环、更低的放电率和更高的单节电池工作电压(3.6V)。显然,锂离子电池的高工作电压将有利于减小移动装备的尺寸,高能量密度将有利于电池的轻量化,低放电率也能保证存储期间的正常使用。

这十几年间,锂离子电池的应用获得了巨大发展,现已成为通讯类电子产品的主要能源之一,被广泛应用在笔记本电脑、GSM/CDMA、数码相机、摄像机及PDA等高端便携式消费类电子产品中。如果将1997年以前适应笔记本电脑市场、降低电池成本、提高容量称为锂离子电池第一个黄金时期,那么在手机、摄像机等便携电子产品的普及将使锂离子电池产业进入第二个黄金时期。比如,2004年94%的手机电池是锂离子电池。随着技术的发展,对锂离子电池的需求将日益旺盛,2005年预计达12亿只。从锂离子电池的生产和销售分布来看,在2000年以前,日本是锂离子电池的最大生产和销售国,市场占有率达到95%以上。但近年来随着中国和韩国的迅速崛起,日本一支独秀的格局已经被逐渐打破,预计2005年日本锂离子电池的全球市场占有率将跌至50%以下。

2、锂离子电池管理芯片的重要性

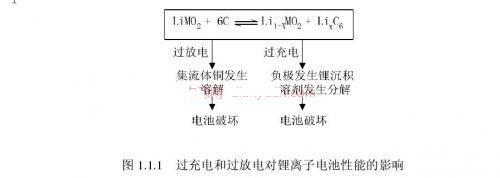

在锂离子电池的研究开发中,提高使用安全性问题一直是研究的重点。由于质量比能量高,而且电解液大多为有机易燃物等,当电池热量产生速度大于散热速度时,就有可能出现安全性问题。有研究指出,锂离子电池在滥用时,有可能达到700°C以上的高温,从而导致电池出现冒烟、着火乃至爆炸;在过放电到低于1V时,正极表面将析出铜,造成电池内部短路;在过流情况下,电池内部温度也极易升高,使电池性能恶化乃至损坏。图1.1.1给出了在过充电和过放电情况下,锂离子电池内部的化学反应及性能的变化,式中M代表Co、Al、Ni等金属离子。

要提高锂离子电池使用的安全性,除了进行深入的机理研究,选择合适的电极材料及优化整体结构之外,还必须通过电池外围的集成电路(IC)对电池进行有效的管理。有报道称近年来,电池管理(Battery Management)芯片,无论是销售额还是销售量在功耗管理(Power Management)芯片中有望增长得最快。锂离子电池管理目标包含对电池电压监测、充放电电流监测、温度监测、数据计算以及存储。管理芯片中,包括保护电路、燃料检测电路以及能够实行电池数据传输的系统被称为智能电池系统(Smart Battery System,SBS)。SBS电池组结构如图1.1.2所示,它由温度传感器、能检测双向电流的电流检测器、ADC、EEPROM存储器、时钟、状态/控制电路、与主系统单线接口及地址、锂离子电池保护电路等组成。其中由ADC转换的数字量存储在相应的存储器内,通过单线接口与主系统连接,对内部存储器进行读/写的访问及控制。SBS除了能对电池进行有效地保护之外,还能输出电池剩余能量信号(可用LCD显示),这将是锂离子电池管理芯片发展的主要目标。目前,SBS应用的协议发展到了SBdata1.1(数据协议)和SMbus2.0(总线协议),而在IBM和索尼等笔记本电脑中,有几个型号已采用了基于电池保护电路的SBS.。

在锂离子电池管理芯片中,保护电路由于能够实现对电池电压、充放电电流监测,它既能单独内置在锂离子电池中,也能在SBS中充当二次保护电路用,更可贵的是,它能实现对Ni-Cd、Ni-H电池的同等保护,所以在电池管理芯片中占了很大的份额。

3、电池管理芯片的发展现状

目前,国外的Unitrode、Texas、Dallas等公司纷纷开展了对锂离子电池管理芯片的研究和开发。和电池产量在全球市场占有率不断下滑不同的是,日本的锂离子电池管理芯片,尤其是保护电路的设计开发,始终在全球占有主导地位。最著名的产品是精工的S82系列、理光的R54系列和MITSUMI的MM3061系列等。其中,S82系列产品因为功能齐全、精度高和功耗低,被认为是锂离子电池管理芯片设计的领跑者之一。而在中国,除了台湾有个别单位已开发出了功能较为简单的保护芯片外,近年来,虽然也有个别大陆单位开始研究锂离子电池保护电路,但都处于起步阶段,精度低、没有统一的保护标准。更主要的是,目前国内还没有具有独立自主产权的电路出现。

目前,为了在最长的电池使用时间和最轻的重量之间取得平衡,越来越多的便携式设备如手机、摄像机等都采用单节锂离子电池作为主电源。目前单节锂离子电池的管理芯片研究,重点在于:

①除了要对电池充电过程进行有效管理外,还更迫切地需要实现对充电及使用过程的全程保护。这要求芯片不仅具有完备的保护功能,而且保护精度如电池电压、延时时间的检测和控制精度达到实用要求。

②应该尽可能地降低功耗以延长供电电池的使用寿命。作为封装后电池的一部分,芯片的驱动始终来自被管理的电池,因此要求芯片要有足够低的电流消耗。

作为一个数模混合信号电路,可以借鉴已有的一些功耗优化方法,但是结合应用特点降低功耗,还要进行更深入的理论探索。

因此,研究以单节锂离子保护电路为代表的电池管理芯片的低功耗,从系统功能实现到数模混合信号电路低功耗的设计,对电池管理芯片的设计乃至SBS的开发都将有相当的借鉴作用。

|

||||||

|

||||||