摘要

所有便携式电子设备,例如手机、收音机、数码相机及手提电脑等都需要依赖电池来维持电力,为了维持这些电子设备持续工作,必须反复地经由市电通过充电器来对电量耗尽的电池进行充电。而这样大家习以为常的电池充电过程却在无形中带来能源耗损,所以需要创新的技术来降低无谓的能量消耗。特别是在待机的时候可以达到节能法规的要求,例如美国加州能源委员会(California Energy Commission, CEC)节能规范,以及能源之星(Energy Star)标识计划等,因此本篇文章将会探讨一个新型极低待机功耗的电源控制IC。

飞兆半导体新推出的FAN302HL驱动控制IC,在手机充电器的应用中可达到低于10mW的待机能源消耗,并且结合多项领先技术来提升低功率反激式转换器的性能,如:内建高压激活电路、待机时的低工作电压与工作电流,采用次级端反馈控制方法调节固定输出电压,初级端反馈控制方法调节固定输出电流。FAN302HL将会成为在待机时的极低功耗电源控制IC设计最好选择。

简介

油价飞涨,原物料价格屡创新高,全球能源管里濒临崩溃边缘,“节约能源”再次成为最热门的议题。而在环保的观念持续强化下,现代人对于日常节约能源的观念越来越健全,但节约能源除了把不用的电器关闭或是采取定时开关方式节约能源外,其实这些电子装置本身因电源电路设计的限制。平日开启运作及待机的电源功耗日益增多,使得能源的应用效率低下,有效的电源管理,才能让“节能”的效益更加立竿见影。电源管理方面最重要的趋势,就是使待机功耗降至最低。一般可能认为,与工作时电源的耗电量比起来,电子设备待机时所消耗的电量是微乎其微。其实这与事实相去甚远,所以美国加州能源委员会(California Energy Commission, CEC)节能规范,以及能源之星(Energy Star)标识计划等,在所有电源的规划当中,对于“待机功耗”的规范极为重视。因此在国际能源总署(IEA)的推动和倡导下提出“1瓦计划”的能源规划,目标是到2010时将大部份电器产品的待机功耗降到1瓦,而美国也在2007年12月颁布了“2007美国能源独立与安全法案”,为消费类电器设备制定了第一个强制性的联邦能源标准。

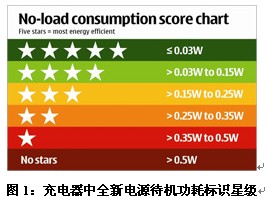

其中令人注目的是在2008年11月世界主要手机供货商公布的新手机充电器的待机规范,明确定义出不同的待机功耗有不同的标识星级,如图1所示为新手机充电器的待机功耗标准,其中最高五颗星的待机功耗必须降低至30mW以下,因此,要如何使电源转换器达到更低的待机功耗,将会是电源设计工程师未来所需要迎接的挑战。

FAN302HL待机功耗来源分析与低待机功耗解决方案

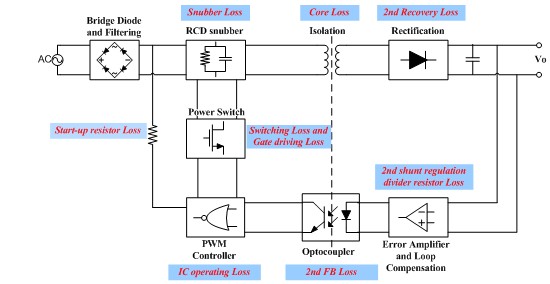

如何使FAN302HL的待机功耗降低到30mW以下,甚至达到更低10mW,以下会有详细的分析介绍。首先可以先以基本常用的反激式转换器的电源架构来做分析,如图2所示。

图2:典型的反激式转换器电路

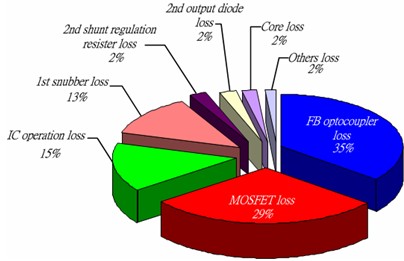

图3:待机功耗各部份的分析示意图

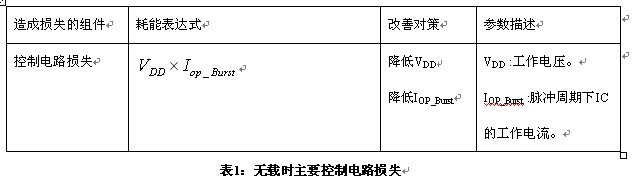

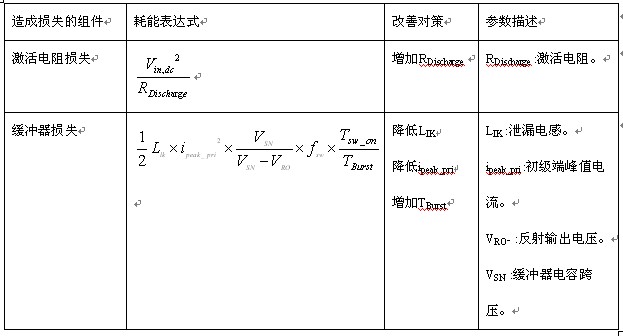

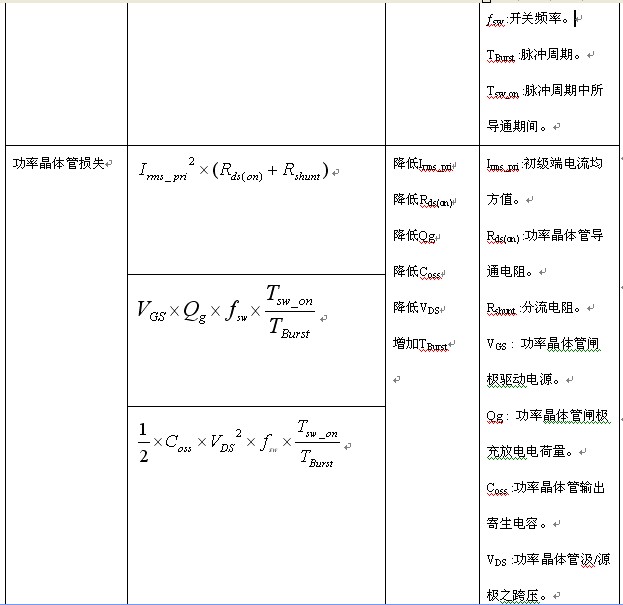

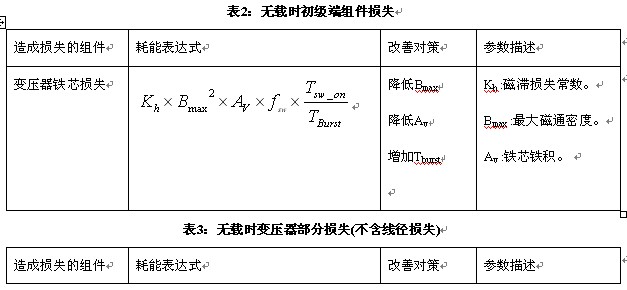

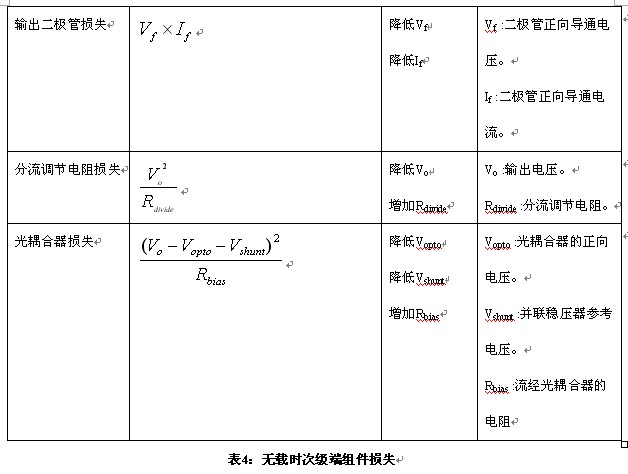

从图3可看出待机功耗的分布,对一个反激式转换器而言,主要的待机功耗包括了开关功耗(switching loss)和传导功耗(conduction loss)以及PWM控制电路所造成的功耗。表1、表2、表3、表4分别对这些主要功耗,列出估算公式与改善对策。

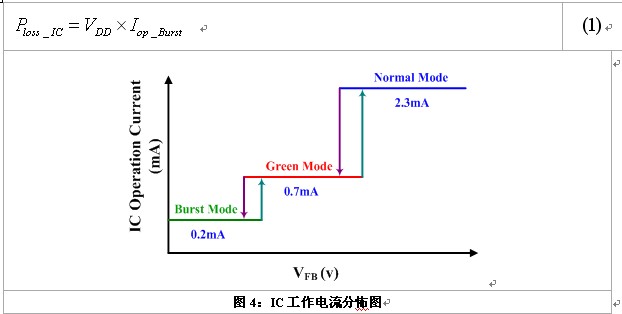

1、控制电路损失(15%):由表1与等式(1)中可知,在待机时为了使PWM IC维持正常的工作,在辅助线路设计上必须确认能够提供足够的电压供应(VDD),由于FAN302HL的最低工作电压(VDD_OFF)为5V,所以通常设计在7V附近最为理想。而在PWM IC工作电流方面,FAN302HL拥有多段的电流工作控制,如图4所示,当工作在脉冲模式(Burst mode)时,会以极低的工作电流,来降低FAN302HL的待机功耗。

2、初级端组件损失:由表2中可知,初级端组件损失主要是由激活电阻损失、缓冲器损失与功率晶体管(Power MOSFET) 损失的总和。

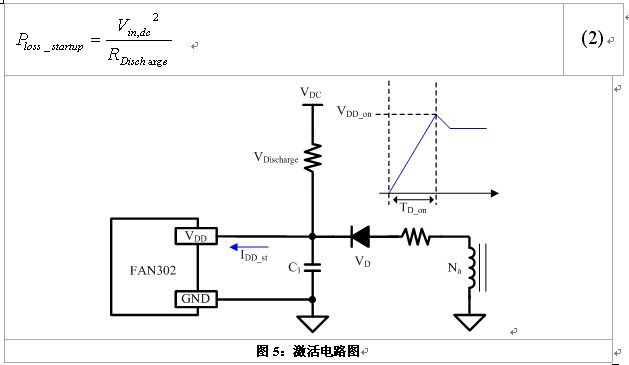

激活电阻损失(1%):为了使PWM IC在正常工作前能获得电源电压,通常会设置有激活电路,如图5,所示,但PWM IC从辅助绕组获得电源供应之后,激活电路便失去作用,但此时激活电阻上的跨压仍然会持续造成功耗,等式(2)所示,FAN302HL内建高压激活电路(HV)代替传统激活电路的设置,可减少激活电阻造成的功耗并可加速开机时间与高压的激活能力。

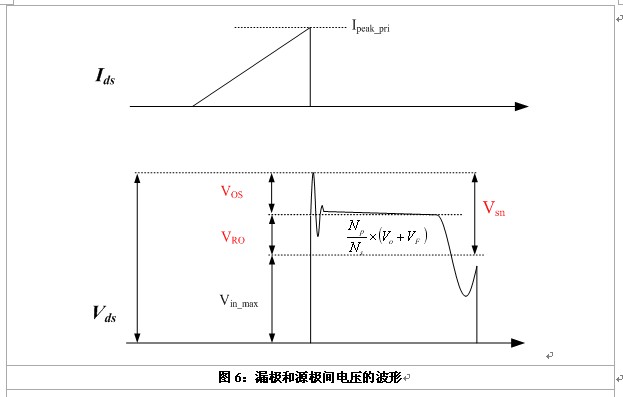

缓冲器损失(13%):当功率晶体管关闭的同时,会在漏极/源极之间的电压(VDS)上产生较高的尖峰电压,如图6所示,这是由于变压器上的泄漏电感所导致,因此避免泄漏电感的产生与峰值电流的增加,就能有效地改善消耗损失,如等式(3)

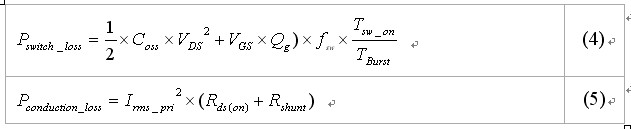

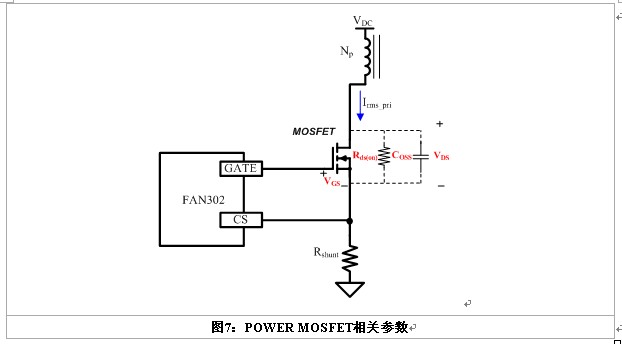

功率晶体管损失(29%):在功率晶体管损失的部份中,主要包含了开关与传导损失,如等式(4)(5)所示,而在手机充电器的应用中又以开关损失占大多数,因此除了挑选合适的功率晶体管外,经由脉冲模式(Burst mode)技术,减少单位时间内功率晶体管的开关次数来降低开关损失并维持输出电压的稳定,可有效改善此部份的功耗,图7为Power MOSFET相关参数。

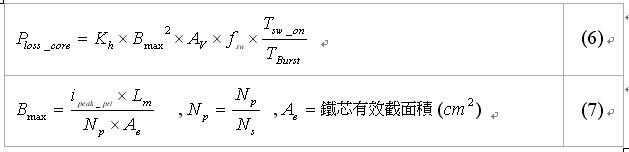

3、变压器铁芯损失(2%):变压器传输电能时的消耗主要分为铜损和铁损,铜损是初级端电流流经变压器线圈阻抗上造成的耗损,但是在空载待机的情况下流经变压器线圈上的电流很小,因此在此条件下铜损的影响可被忽略。表5与等式(6)所列为铁损的功耗公式,从式中可知降低开关频率与磁通密度可以改善铁芯损失,而调整磁通密度时,势必会提高匝数比,而线圈匝数增加也会导致铜损上升,如等式(7)所示,因此需要合理的设计磁芯的磁通密度和工作频率来达到功耗的改善

4、次级端组件损失:由表4中可知,次级端组件损失主要是由输出二极管、分流调节电阻与光耦合器损失的总合。

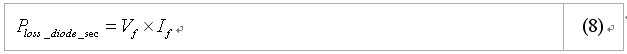

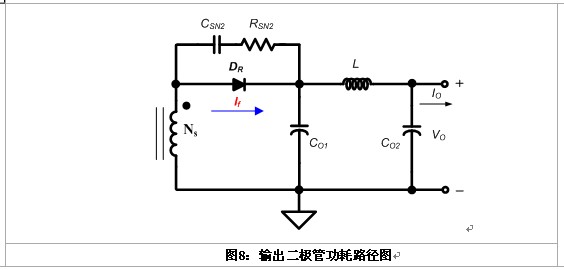

输出二极管损失(2%):图8所示为输出二极管功耗路径,当电流在流过二极管为正向时,会与PN两极体上所产生的正向导通电压来造成损失,如等式(8)所示,因此挑选较低正向导通电压的输出二极管是必备条件之一。

分流调节电阻损失(2%):由于在分流调节器必需经由分流调节电阻来导通动作并与参考电位来做比较,以达到恒定输出电压,但此调节电阻仍会占据少量功耗,如等式(9)所式,因此提高调节电阻可以有效改善功耗,但同时也会影响到反馈稳定度,因此在这部份的取舍也是要仔细考虑,图9为功耗路径。

光耦合器损失(35%):光耦合器用来提供次级端到初级端间的讯号传递并免于噪声干扰,同时也提供了稳压控制的讯号路径,经由电流限制电阻器(Rbias)来提供光耦合器正常工作电流,以达到稳定的工作,但是所流经的电流限制电阻器也会对系统造成一定的功耗产生,如等式(10)所式,因此这部份的取舍也需要好好考虑,路径图如图9所示。

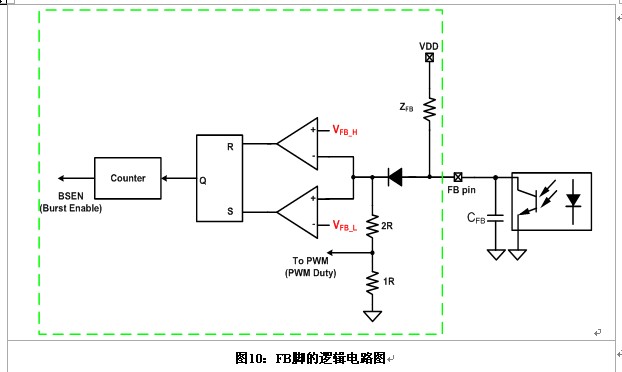

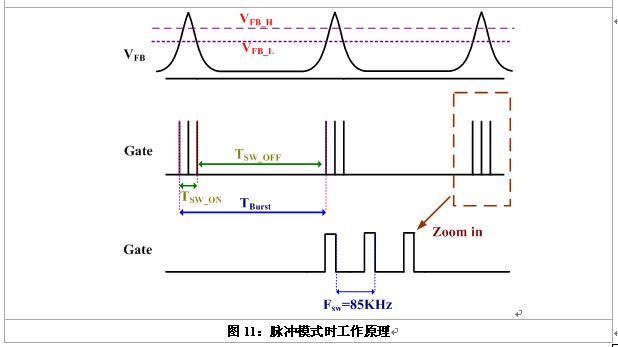

由上述的论述可以很明显的看出,无论是开关功耗(switching loss)和传导功耗(conduction loss)或是由PWM控制电路所造成的功耗,大部份都与开关频率有很密切的关系,因此需要更有效的控制待机时所产生的功耗。FAN302HL采用脉冲模式(Burst mode)的技术,来达到省电的效果。FAN302HL所使用的方式为依据FB引脚的电压变化来判断脉冲模式的导通周期,达到在无载时的极低待机功耗,从图10中可知FB引脚除了PWM任务调节外,也负责脉冲模式任务的调节。当IC工作在脉冲模式时FB引脚会判断该电压准位所发生的动作,当VFB低于VFB_L时,会去强制关掉PWM输出,使之无能量供给,增加脉冲周期,此时输出电压会有些下降,因而VFB很快提高,所以当VFB高于VFB_H时会在强制导通PWM,以供给输出能量,借用如此交替的运作来达到合适的脉冲模式调配。从图11中可看到脉冲模式时的动作原理与脉冲模式时的相关参数。

FAN302HL无载待机功耗计算实例

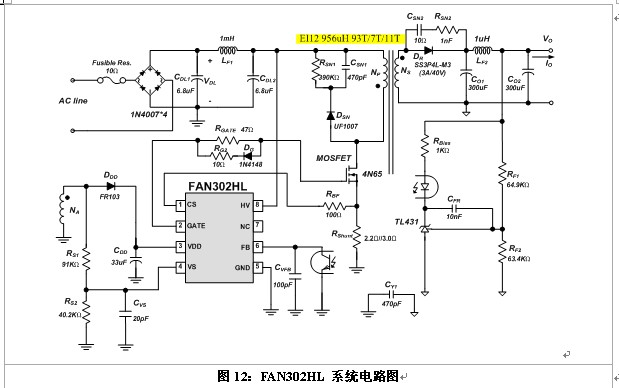

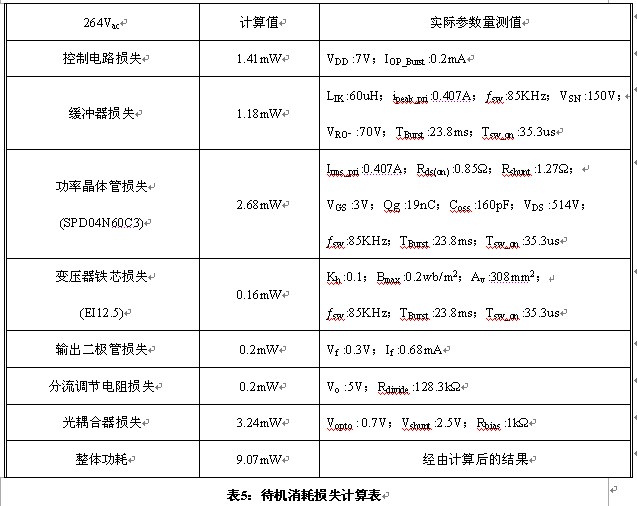

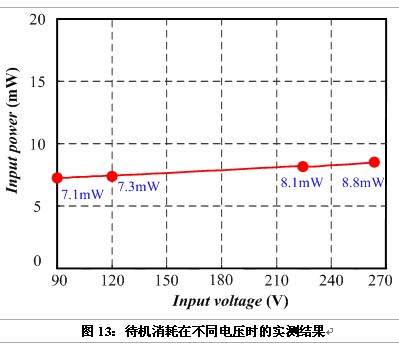

使用飞兆半导体所研发出的节能PWM IC;FAN302HL,放置于测试板上,如图12所示(其额定输出电压与电流规格为5V/1A),测量条件为;输入264V交流电压并工作在无载,并由表5所计算出功耗值,待机功耗约9.07mW。此结果与系统实际测试结果相差不多,图13为系统实测结果图。

结论

在电源领域,已越有越来越多对于极低待机功耗的产品需求,因此本文主要针对飞兆半导体新推出的FAN302HL驱动控制IC来探讨降低电源整体待机功耗的方法。以数学表示式计算出主要的开关和控制电路损失,并介绍用多项飞兆半导体创新的专利技术去实现更低的整体待机功耗。最后在额定输出电压/电流规格为5V/1A,264V交流输入且输出无载时,使待机功耗可以达到小于10mW的结果。此外FAN302HL驱动IC除了可以实现极佳的节能控制外,也可实现高频工作(85KHz)与高效率工作,绝对可以满足手机充电器的应用,达到“轻薄短小”的目标。

|

||||||

|

||||||